The conventional SDRAM modules and DDR SDRAM modules have the same basic lines, as can be seen in this picture. It is still difficult for the uninitiated to spot the difference between the two DIMM's. SDRAM (above) has two notches, whereas DDR SDRAM (below) only has one. If you have an MSI Pro266 Master or a Shuttle AV32, it's a good idea to take a good look at your board slots. Both boards have SDR DIMM slotsand DDR DIMM slots. It's easy to confuse the two if you don't pay close attention to the notches.

SDRAM [Synchronous Dynamic Random Access Memory]

- a type of DRAM that runs in synchronization with the memory bus. SDRAM delivers information in very high-speed bursts using a high-speed, clocked interface. SDRAM removes most of the latency involved in asynchronous DRAM because the signals are already in synchronization with the motherboard clock.

- dramatically improved over that of FPM or EDO RAM. Because SDRAM is still a type of DRAM, the initial latency is the same, but overall cycle times are much faster than with FPM or EDO. SDRAM timing for a burst access would be 5-1-1-1, meaning that four memory reads would complete in only eight system bus cycles, compared to eleven cycles for EDO and fourteen cycles for FPM. This makes SDRAM almost 20% faster than EDO.

DDR SDRAM

Compared to single data rate (SDR) SDRAM, the DDR SDRAM interface makes higher transfer rates possible by more strict control of the timing of the electrical data and clock signals.

Backward compatibility

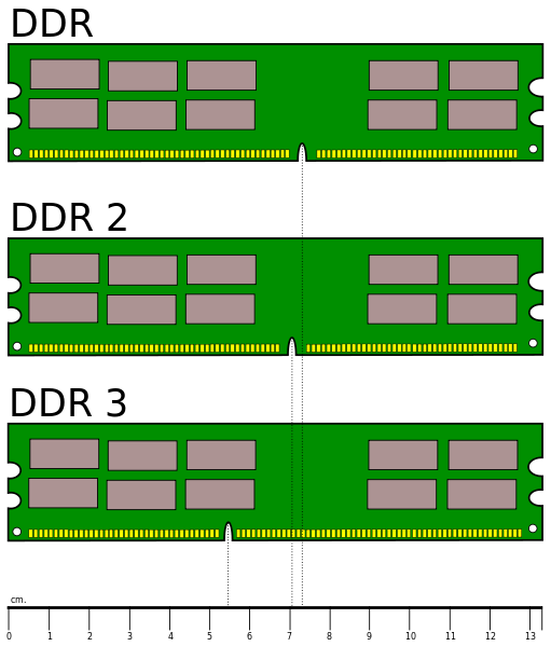

DDR2 DIMMs are not designed to be backward compatible with DDR DIMMs. The notch on DDR2 DIMMs is in a different position from DDR DIMMs, and the pin density is higher than DDR DIMMs in desktops. DDR2 is a 240-pin module, DDR is a 184-pin module. Notebooks have 200-pin modules for DDR and DDR2, however the notch on DDR modules is in a slightly different position than that on DDR2 modules.

Higher-speed DDR2 DIMMs are compatible with lower-speed DDR2 DIMMs although the motherboard or CPU memory controller will be bound to the limits of the lower-performance modules.

RSS Feed

RSS Feed